- 服务热线: 138-1706-5520

台积电A14亮相,FinFET 到 GAA未来芯片如何散热?

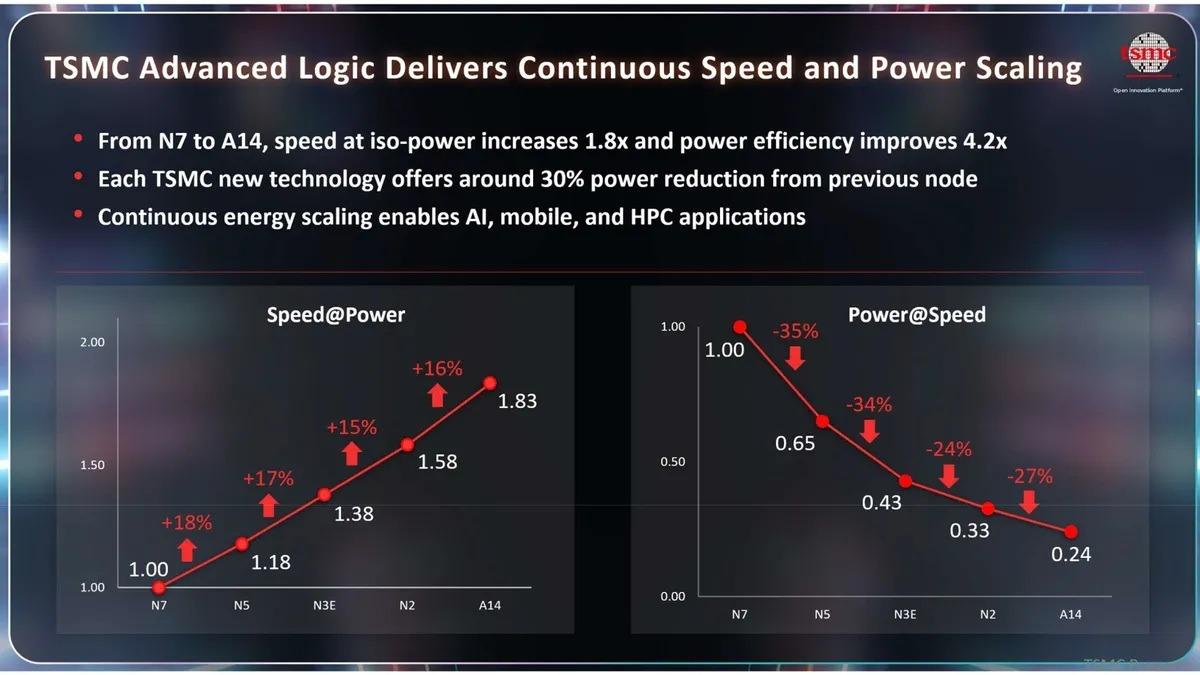

近日台积电在欧洲 OIP 论坛上展示了 A14 制程的最新数据:在相同功耗和复杂度下性能提升可达 16%,在相同频率下功耗下降约 27%。这意味着晶体管的尺寸再次被推向极限,制程继续朝着“更小、更密集、更节能”的方向迈进。随着 A14 计划在 2028 年量产,先进工艺的竞赛也进入一个全新的阶段。

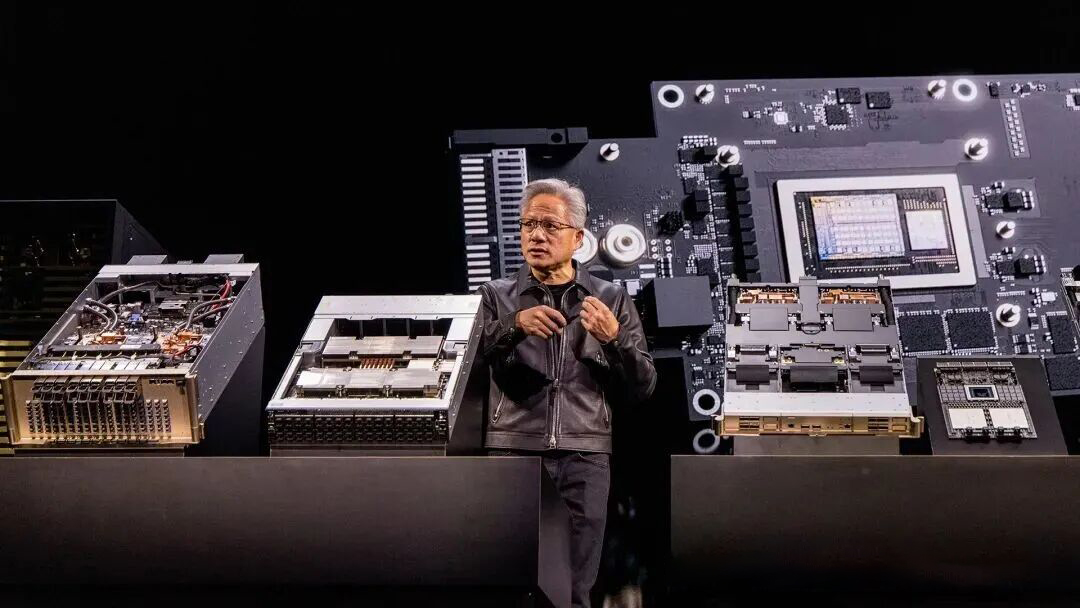

当前AI芯片的发展从根本上是出于对更高性能的追求,但这也带来了一个关键的挑战“热管理”。随着性能不断提高,“热管理”正成为一个无法回避的核心挑战:如何有效散出功耗增加带来的大量热量,已经逐渐变成影响芯片架构设计的重要因素,也是不少芯片厂商面临的现实难题。

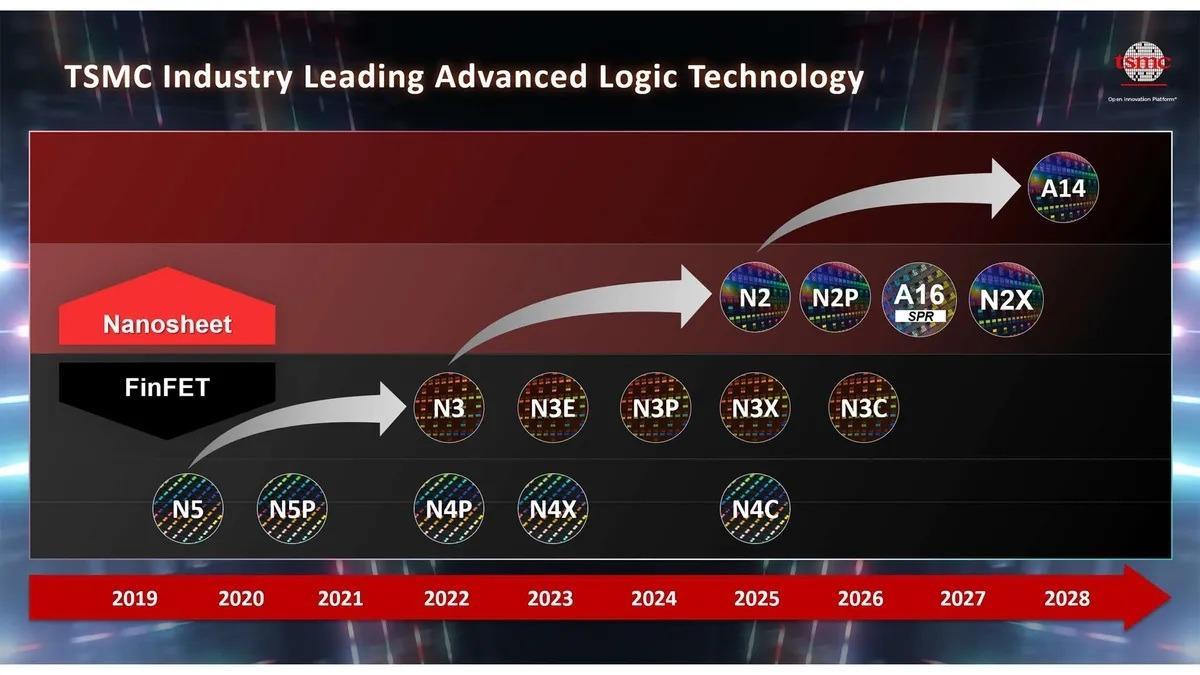

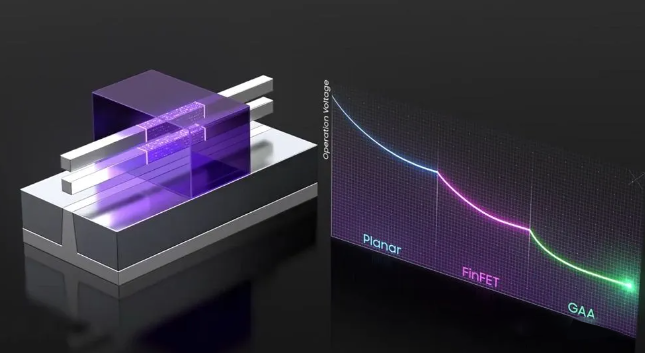

在逻辑工艺方面,以台积电为代表的英伟达系列AI 芯片从N3→N2→A16→A14的演进,这个过程涉及的不仅仅是尺度上的几何缩放,也代表了晶体管架构的转变:从FinFET,到GAA(Gate-All-Around),这一系列变化旨在实现PPA(功率、性能和面积)的最佳平衡,为高效的AI计算奠定基础。

那么,“A14”到底意味着什么?为什么制程越做越小,芯片却越来越难散热?要理解这些问题,我们需要从沙子开始讲起——从现在的 FinFET,到下一代的 GAA。借着 A14 的机会,小编也和大家一起重新回顾一下芯片制造。目前整个集成电路产业链可划分为设计、晶圆制造(前道工艺)和封装测试(后道工艺)三个主要环节。今天我们重点围绕前道和后道工艺做个介绍。

1.芯片怎么制造?

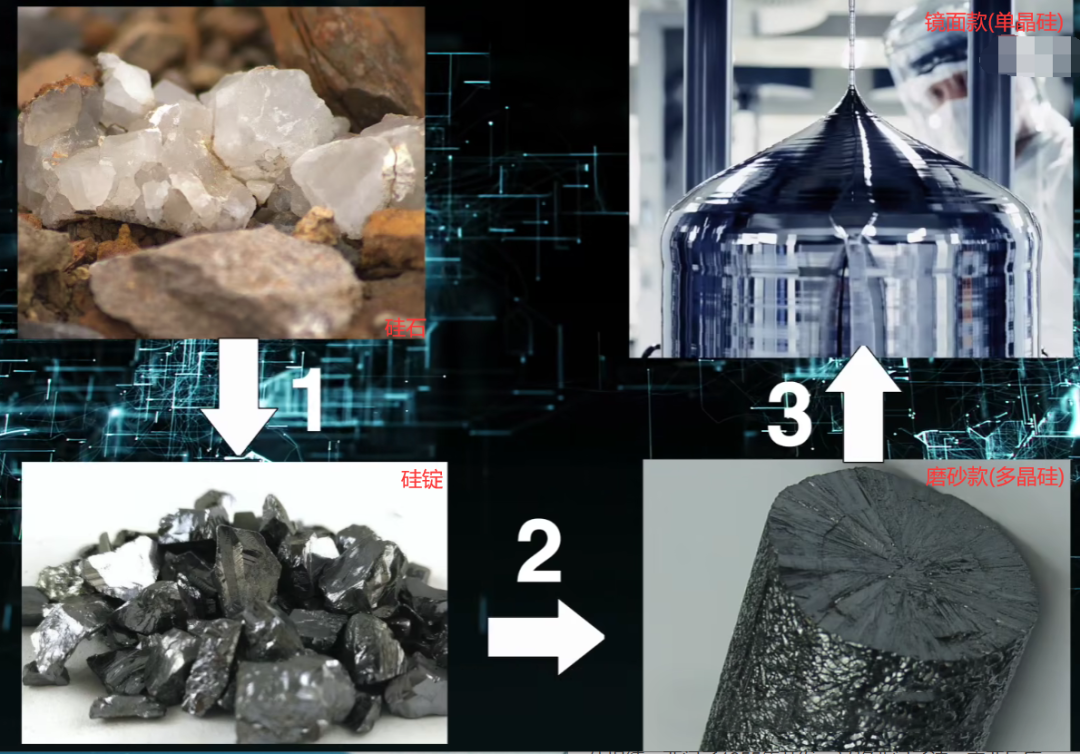

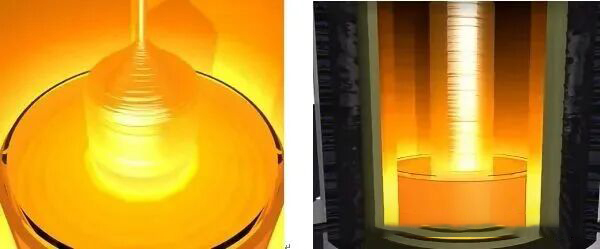

大家应该看过很多诸如“沙子造芯片”类型的视频或者科普文章。没错,目前主流的芯片都是以硅Si基芯片为代表,沙子的成分主要是以二氧化硅SiO2为主,因此就有了很多关于沙子和芯片的故事。制造芯片的第一步就是提纯通过高温加热还原出硅,我们就得到了多晶硅。

在集成电路中我们需要的是单晶硅,多晶硅中的杂志含量太高无法满足集成电路的使用要求,通常我们需要9N-11N纯度的单晶硅。这一步常用的方法有柴可拉斯基法又称直拉法(CZ)和区域熔融法(FZ);目前约85%的硅片由直拉法生产,15%的硅片由区域熔融生产。按应用分直拉法生长出的单晶硅,主要用于生产集成电路元件,而区熔法生长出的单晶硅主要用于功率半导体。

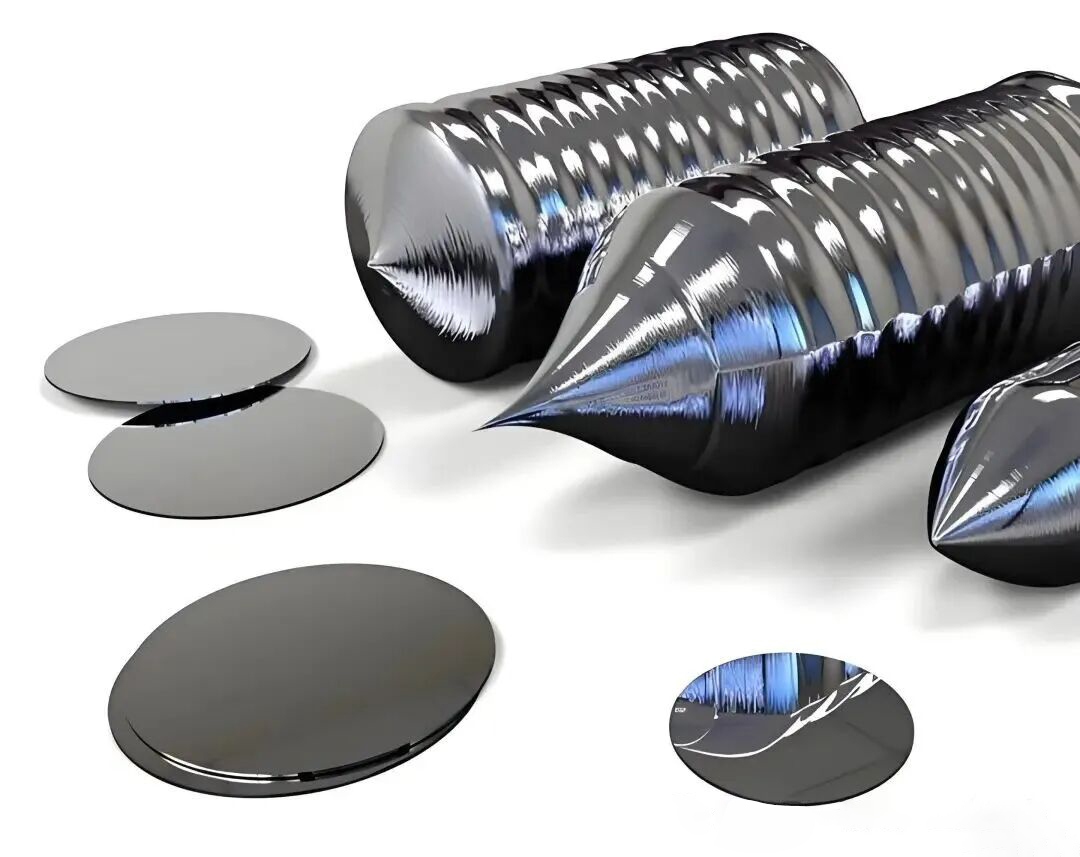

通过提拉法得到晶棒之后,再通过切割-滚磨-定位边研磨-切割-清洗-倒角/磨边-研磨-清洗/刻蚀得到粗硅片;再通过化学机械抛光-清洗-检验就得到了“硅片”。常用的有外延片、退火片、SOI硅片、结隔离片等;常见的单晶硅片直径8-19英寸,目前主流6(150mm)、8(200mm)、12(300mm)英寸。

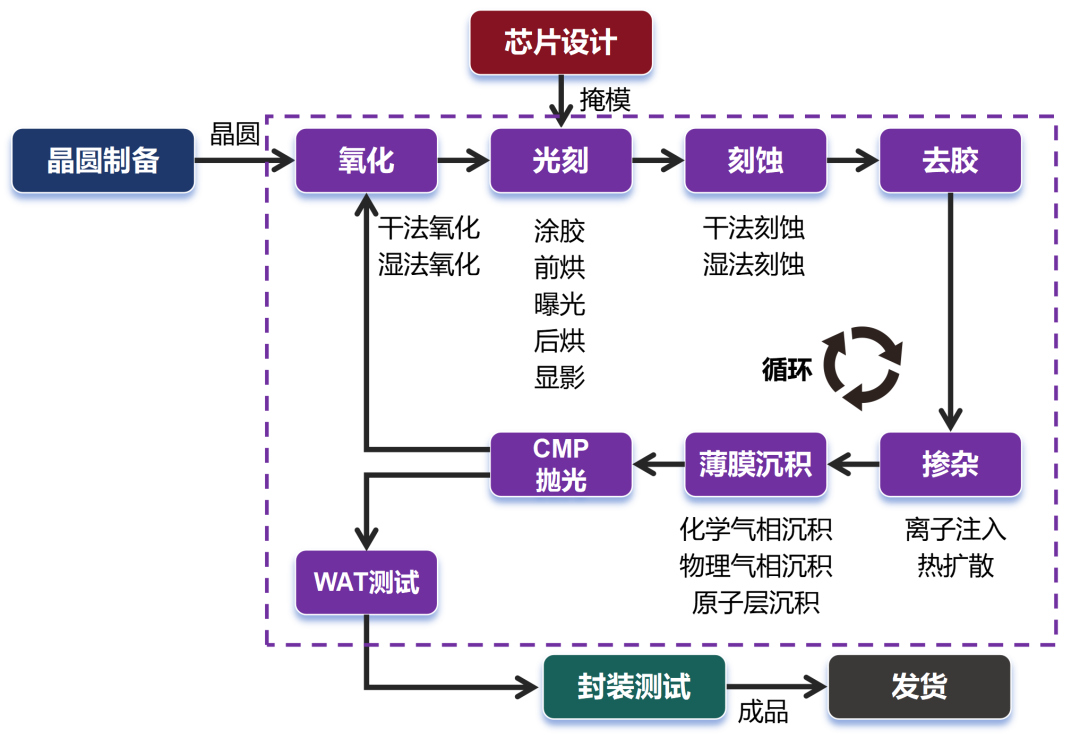

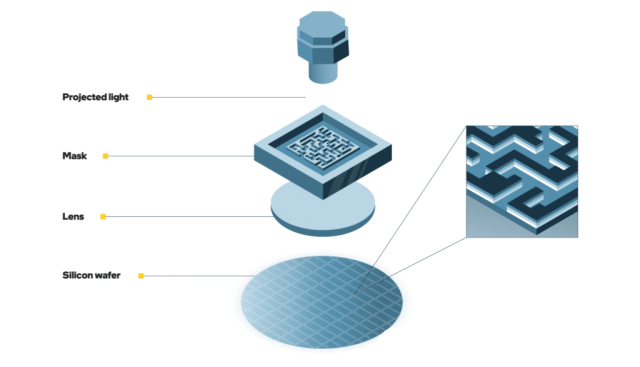

接下来我们继续前道的工艺,有了单晶硅片接下来晶体管都是被通过什么工艺刻在上面。工程师通过氧化-涂胶-曝光-显影-刻蚀-去胶-涂胶-掺杂-薄膜沉积-化学机械抛光等工艺流程;

整个过程需要重复多次,形成数百层复杂结构。每一层都是微观建筑的一部分,最终在指甲盖大小的芯片上排列出几百亿个晶体管。这些晶体管通过金属互连形成完整的逻辑电路,使芯片能够完成计算、存储和通信等任务。

2.关于“晶体管”

晶体管是让计算机芯片工作的微型开关。没错,就是开关。现代芯片本质上是大量微小晶体管的集合。虽然它们看似简单,但晶体管是现代计算机的基础——被认为是历史上最重要的发明之一。

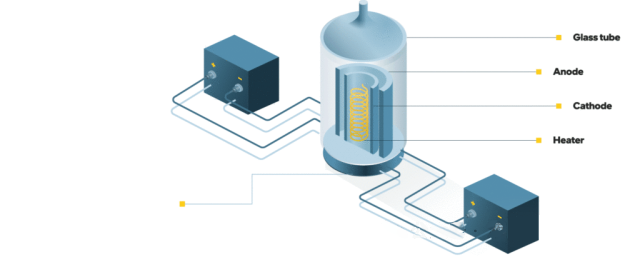

在 20 世纪,计算机先驱们探索了各种用于计算和存储数据的设备,最终形成了二进制系统与真空管的组合。二进制允许将信息编码为 0 和 1——开或关,而真空管则是第一个可靠的电子开关。这些“比特”成为现代计算的基石。第一台可编程电子计算机 ENIAC(1945 年)使用了 18,000个真空管,但这些管子耗电量大、容易发热且容易损坏,导致系统经常宕机。显然,需要更小、更可靠的开关。

1947 年贝尔实验室首次展示晶体管,它迅速取代了真空管,成为节能且可靠的电子开关。随后MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)出现,通过在硅上构建受控氧化层,实现了高效的平面电路制造。光刻技术在这一过程中至关重要——工程师通过曝光、刻蚀等工序,在晶圆上精确排列晶体管,为后续的复杂电路打下基础。

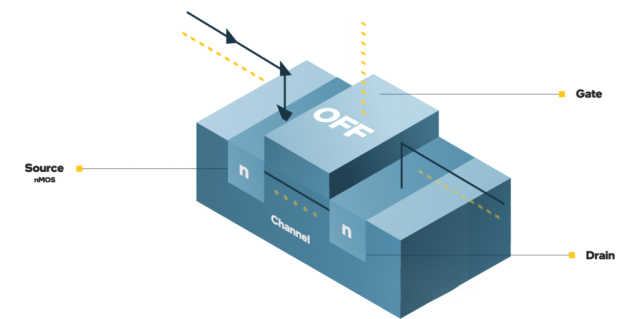

每个 MOSFET 由源极和漏极组成,电流在通道中流动,由栅极控制通断。栅极施加电压即可吸引通道内的电荷,实现电流开关。nMOS 与 pMOS 晶体管组合成 CMOS,用于构建各种逻辑电路,从简单加减法到复杂的 AI 计算。

3.FinFET 到 GAA:晶体管结构的演进与热管理挑战”

芯片之所以会发热,根源在于其内部成千上亿个晶体管在不断地“开”和“关”。在这个过程中,一部分电能不可避免地转化成热能。一个芯片中可能包含数十亿、甚至超过一万亿个晶体管。在摩尔定律不断逼近物理极限的背景下,晶体管结构也在经历代际更替。从Planar(平面晶体管)到FinFET(鳍式场效应晶体管)已经在十几年内主导了芯片工艺的主流路线,通过设计、材料、制造、封装各类技术的推进摩尔定律也得以持续推进。

4.总结

随着AI芯片计算能力不断提升,其内部成千上万亿个晶体管产生的热量也越来越集中,传统风冷和普通液冷已难以应对。芯片热量的传递涉及硅衬底、金属互连、微凸块、热界面材料等多层结构,层层热阻导致局部“热点”成为限制性能的关键因素。为解决这一问题,业界开始采用高导热材料如碳化硅(SiC)、金刚石薄膜和铜-金刚石复合材料,以缩短热路径、降低界面热阻,同时通过微通道液冷技术(MCL/MLCP)显著增加流体与芯片接触面积,实现高功率密度下的高效散热。台积电和英伟达在这一领域采取不同策略,但目标一致:通过材料优化、封装创新与液冷技术结合,使未来AI芯片在千瓦级功耗下仍能稳定运行,推动热管理从传统工程手段演进为决定芯片性能与竞争力的核心技术。

联系我们

Contact us

地址:上海市浦东新区宣秋路139号1号楼

邮编:201315

总机:021-68061048

直线:138-1706-5520

传真:021-68061042

邮箱:info@kekun.com.cn

添加微信